## **Low Latency Audio Processing**

### Yonghao Wang

School of Electronic Engineering and Computer Science

Queen Mary University of London

2017

Submitted to University of London in partial fulfilment of the requirements for the degree of

Doctor of Philosophy

Queen Mary University of London

**Statement of Originality**

I, Yonghao Wang, confirm that the research included within this thesis is my own work

or that where it has been carried out in collaboration with, or supported by others, that

this is duly acknowledged below and my contribution indicated. Previously published

material is also acknowledged below.

I attest that I have exercised reasonable care to ensure that the work is original, and does

not to the best of my knowledge break any UK law, infringe any third party's copyright

or other Intellectual Property Right, or contain any confidential material.

I accept that the College has the right to use plagiarism detection software to check the

electronic version of the thesis.

I confirm that this thesis has not been previously submitted for the award of a degree by

this or any other university.

The copyright of this thesis rests with the author and no quotation from it or information

derived from it may be published without the prior written consent of the author.

Signature:

Date: 28/November/2017

2

#### **Abstract**

Latency in the live audio processing chain has become a concern for audio engineers and system designers because significant delays can be perceived and may affect synchronisation of signals, limit interactivity, degrade sound quality and cause acoustic feedback. In recent years, latency problems have become more severe since audio processing has become digitised, high-resolution ADCs and DACs are used, complex processing is performed, and data communication networks are used for audio signal transmission in conjunction with other traffic types. In many live audio applications, latency thresholds are bounded by human perceptions. The applications such as music ensembles and live monitoring require low delay and predictable latency. Current digital audio systems either have difficulties to achieve or have to trade-off latency with other important audio processing functionalities.

This thesis investigated the fundamental causes of the latency in a modern digital audio processing system: group delay, buffering delay, and physical propagation delay and their associated system components. By studying the time-critical path of a general audio system, we focus on three main functional blocks that have the significant impact on overall latency; the high-resolution digital filters in sigma-delta based ADC/DAC, the operating system to process low latency audio streams, and the audio networking to transmit audio with flexibility and convergence.

In this work, we formed new theory and methods to reduce latency and accurately predict latency for group delay. We proposed new scheduling algorithms for the operating system that is suitable for low latency audio processing. We designed a new system architecture and new protocols to produce deterministic networking components that can contribute the overall timing assurance and predictability of live audio processing. The results are validated by simulations and experimental tests. Also, this bottom-up approach is aligned with the methodology that could solve the timing problem of general cyber-physical systems that require the integration of communication, software and human interactions.

## Acknowledgements

Firstly, I would like to express my sincere gratitude to my supervisor Professor Josh Reiss for his continuous support of my PhD work, for his patience, precision, motivation and wide knowledge. My sincere thanks also go to Professor Cham Athwal, who supports me to prioritise research and other commitments in the workplace. I'd like to thank all the colleagues in the Centre for Digital Music at the Queen Mary University of London and the DMT Lab at the Birmingham City University for their inspirations and collaborations. Many thanks to my PhD examiners Professor Rob Toulson and Dr Andrew McPherson, for their valuable advice and inspiration discussions. Finally, I would like to thank my family, parents, wife, and two lovely children for supporting me throughout eight years of work in this research area.

## **Contents**

| 1 | Intr | oduction                                         | 17 |  |  |  |

|---|------|--------------------------------------------------|----|--|--|--|

|   | 1.1  | Motivation                                       | 17 |  |  |  |

|   | 1.2  | Aim and Objectives                               | 19 |  |  |  |

|   | 1.3  | The Method of Research                           | 20 |  |  |  |

|   |      | 1.3.1 The Systems Engineering Point of View      | 20 |  |  |  |

|   |      | 1.3.2 The Causes of Latency and Latency Taxonomy | 21 |  |  |  |

|   |      | 1.3.3 Reduce the Latency and Design Trade-Off    | 22 |  |  |  |

|   |      | 1.3.4 Report Accurate Latency                    | 23 |  |  |  |

|   |      | 1.3.5 Group Delay and Buffering Delay            | 24 |  |  |  |

|   |      | 1.3.6 Digital Audio System Signal Flow           | 24 |  |  |  |

|   |      | 1.3.7 System Engineering Approach                | 26 |  |  |  |

|   | 1.4  | 4 The Scope of the Research                      |    |  |  |  |

|   | 1.5  | The Organisation of the Thesis                   | 28 |  |  |  |

|   | 1.6  | Contributions                                    | 29 |  |  |  |

|   | 1.7  | Associated Publications                          | 29 |  |  |  |

|   | 1.8  | Unpublished Results                              | 31 |  |  |  |

|   | 1.9  | Other Relevant Publications                      | 32 |  |  |  |

| 2 | Lite | rature Survey                                    | 33 |  |  |  |

|   | 2.1  | Perception of Latency                            | 33 |  |  |  |

|   | 2.2  | Trends in Digital Audio Systems                  | 34 |  |  |  |

|   | 2.3  | Latency In Digital Audio System                  | 37 |  |  |  |

|   | 2.4  | System Latency                                   | 38 |  |  |  |

|   |      |                                                  | 38 |  |  |  |

|   |      | 2.4.2 The System Latency Components              | 39 |  |  |  |

|   |      |                                                  |    |  |  |  |

|   |      | 2.4.3    | GPOS Audio Processing Delay Test                               | 40  |

|---|------|----------|----------------------------------------------------------------|-----|

|   |      | 2.4.4    | Algorithm Latency                                              | 41  |

|   | 2.5  | Delay    | of Digital Filters for High Resolution Audio Conversions       | 43  |

|   |      | 2.5.1    | Delay of $\Delta\Sigma$ ADC/DAC                                | 43  |

|   |      | 2.5.2    | Group Delay Formula                                            | 44  |

|   |      | 2.5.3    | Delay of Non-Recursive Linear Phase (LP) Digital Filters       | 45  |

|   |      | 2.5.4    | Filter Order Estimation Methods                                | 49  |

|   |      | 2.5.5    | The Multirate Multistage Filter System                         | 50  |

|   |      | 2.5.6    | Delay of Linear Phase Multistage System                        | 53  |

|   |      | 2.5.7    | The Minimum Phase System                                       | 54  |

|   | 2.6  | Operat   | ing System Scheduling Latency                                  | 61  |

|   |      | 2.6.1    | GPOS vs RTOS for Audio Processing                              | 62  |

|   |      | 2.6.2    | Multimedia Support on GPOS with Real-Time Features             | 64  |

|   |      | 2.6.3    | Typical Real-time Scheduling Algorithms                        | 66  |

|   | 2.7  | Latenc   | y in Audio Networking                                          | 68  |

|   |      | 2.7.1    | Network Support Real-Time Applications                         | 68  |

|   |      | 2.7.2    | Audio Networking                                               | 71  |

|   | 2.8  | Summ     | ary                                                            | 72  |

| 3 | Dela | ay of Mu | ultistage Filter System in Audio Conversion                    | 74  |

|   | 3.1  | Delay    | of $\Delta\Sigma$ Audio ADC/DAC Converters                     | 76  |

|   |      | 3.1.1    | Motivations of the Work                                        | 76  |

|   |      | 3.1.2    | Latency Test for Hardware Audio Codecs                         | 76  |

|   |      | 3.1.3    | Testing Results and Discussions                                | 79  |

|   | 3.2  | Time I   | Domain Performance of Decimation Filter Architectures for High |     |

|   |      | Resolu   | ation $\Delta\Sigma$ ADC/DAC                                   | 83  |

|   |      | 3.2.1    | Introduction of the Work                                       | 83  |

|   |      | 3.2.2    | Basic Concept of Decimation Filter                             | 84  |

|   |      | 3.2.3    | Group Delay of the Decimation Filter in $\Delta\Sigma$ ADC/DAC | 86  |

|   |      | 3.2.4    | Evaluation Methodology                                         | 87  |

|   |      | 3.2.5    | The Filter Performances Matrix                                 | 90  |

|   |      | 3.2.6    | Filter Design and Group Delay Impact Results and Discussions   | 91  |

|   |      | 3.2.7    | Summary of Group Delay of All Evaluated Filters                | 100 |

|     | 3.2.8    | Compare Cost and Signal to Noise Ratio                           | 101 |

|-----|----------|------------------------------------------------------------------|-----|

|     | 3.2.9    | Conclusion of the Section                                        | 103 |

| 3.3 | Simpl    | lified Model of Analysis Design Parameters of Optimal Multistage |     |

|     | Multin   | rate Filters                                                     | 106 |

|     | 3.3.1    | Description of the Background Theory                             | 100 |

|     | 3.3.2    | Knowledge-Based Search and Lookup Tables                         | 108 |

|     | 3.3.3    | Tradeoff Strategy for Minimisation of Both Area and Computa-     |     |

|     |          | tional Cost                                                      | 114 |

|     | 3.3.4    | Model of Delay of Multi-Stage Linear Phase Filter                | 11: |

|     | 3.3.5    | Formulae of Total Delay of Linear Phase FIR Based Multistage     |     |

|     |          | Design                                                           | 110 |

|     | 3.3.6    | Properties of Delay Formula for Multistage Linear Phase Filter   |     |

|     |          | Design                                                           | 11′ |

|     | 3.3.7    | Simulation Results                                               | 12  |

|     | 3.3.8    | Global Balance Design $D_i$ for Both Cost and Delay for 3-stage  |     |

|     |          | 5                                                                |     |

|     | 3.3.9    | Summary of Contributions                                         |     |

| 3.4 |          | rmance Evaluation of Minimum Phase Multistage Filter             |     |

|     | 3.4.1    | Defining Delay Measurements of MP Filters                        | 12' |

|     | 3.4.2    | The Effects of Corner Frequencies                                | 128 |

|     | 3.4.3    | Group Delay Behaviour of MP Filters With Different Order         | 130 |

|     | 3.4.4    | Quantitative Group Delay Measurements of MP Filters With         |     |

|     |          | Different Order                                                  |     |

|     | 3.4.5    | Summary of MP Filter Evaluations                                 |     |

| 3.5 | Concl    | lusion                                                           | 13: |

| De  | lay of D | OAW on GPOS and New Time Deterministic OS Scheduling             |     |

|     | ameworl  |                                                                  | 13′ |

| 4.1 | Laten    | cy Test of Audio Processing Using Modern DAWs and GPOS           | 138 |

|     | 4.1.1    | Background                                                       | 138 |

|     | 4.1.2    |                                                                  | 139 |

|     | 4.1.3    | Test Results                                                     | 14: |

|     | 4.1.4    | Discussion                                                       | 152 |

|     |          |                                                                  |     |

|   | 4.2 | TDCS     | : A New Scheduling Framework for Real-Time Multimedia       | 156 |

|---|-----|----------|-------------------------------------------------------------|-----|

|   |     | 4.2.1    | How TDCS Relates GPOS and RTOS                              | 156 |

|   |     | 4.2.2    | The Characteristics of Modern Real-Time Multimedia System . | 157 |

|   |     | 4.2.3    | Proposed Scheduling Scheme                                  | 158 |

|   |     | 4.2.4    | Model of Rate Monotonic Tasks                               | 158 |

|   |     | 4.2.5    | TDCS Algorithm                                              | 160 |

|   |     | 4.2.6    | Compare TDCS with Non-Preemptive RMS and RMS                | 163 |

|   |     | 4.2.7    | Using TDCS in Mixed-Criticality System                      | 168 |

|   |     | 4.2.8    | Advantages and Disadvantages of TDCS                        | 171 |

|   | 4.3 | Conclu   | usions                                                      | 172 |

|   |     | 4.3.1    | Summary                                                     | 172 |

|   |     | 4.3.2    | Further Work                                                | 172 |

| _ | ъ.  |          |                                                             |     |

| 5 |     | •        | udio Networking and New Low Latency Audio Networking        | 15/ |

|   |     | hitectur |                                                             | 174 |

|   | 5.1 | _        | n New Low Latency Deterministic Network Protocol: Flexilink |     |

|   |     | 5.1.1    | Motivations                                                 |     |

|   |     | 5.1.2    | Introduction                                                |     |

|   |     | 5.1.3    | The Architecture Design of Flexilink                        |     |

|   |     | 5.1.4    | Ethernet Implementations of Flexilink                       |     |

|   |     | 5.1.5    | Interconnection With Existing Network                       |     |

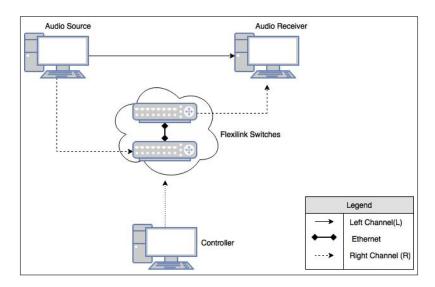

|   | 5.2 |          | ation of the Flexilink Architecture                         |     |

|   |     | 5.2.1    | Motivation of the work                                      |     |

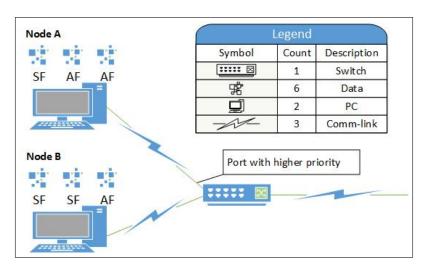

|   |     | 5.2.2    | Simulation Model                                            |     |

|   |     | 5.2.3    | Simulation Overview                                         |     |

|   |     | 5.2.4    | Simulation Scenarios                                        |     |

|   |     | 5.2.5    | Simulation Results Analysis                                 |     |

|   | 5.3 |          | nk Hardware Test                                            |     |

|   |     | 5.3.1    | Hardware Implementation                                     |     |

|   |     | 5.3.2    | Testing Scenarios                                           |     |

|   |     | 5.3.3    | Testing Results                                             |     |

|   | 5.4 |          | usion                                                       |     |

|   |     | 5.4.1    | Summary                                                     | 205 |

|   |     | 5.4.2    | Future Work                                                  | 206 |

|---|-----|----------|--------------------------------------------------------------|-----|

| 6 | Con | clusions | S                                                            | 208 |

|   | 6.1 | Summ     | ary of Main Contributions                                    | 208 |

|   |     | 6.1.1    | Group Delay Caused by Multistage Filters in Audio Conversion | 209 |

|   |     | 6.1.2    | Delay of OS Processing and New Scheduling Framework          | 211 |

|   |     | 6.1.3    | New Audio Networking Architecture                            | 212 |

|   | 6.2 | Critica  | al Assessment of Work                                        | 212 |

|   | 6.3 | Future   | Work                                                         | 213 |

# **List of Figures**

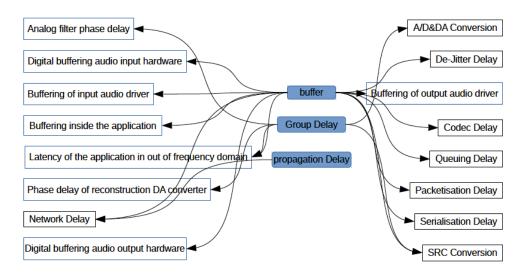

| 1.1  | Different descriptions of the causes of latency in audio systems                   | 21 |

|------|------------------------------------------------------------------------------------|----|

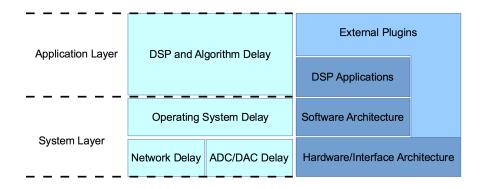

| 1.2  | Different layers of delay in digital audio system                                  | 23 |

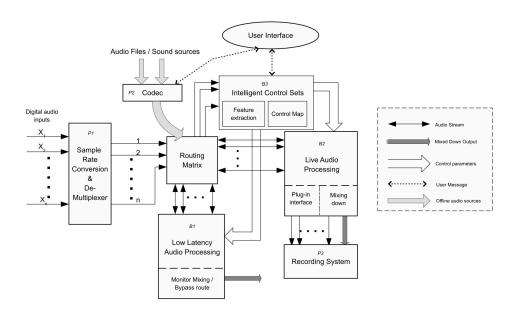

| 1.3  | Digital audio system                                                               | 25 |

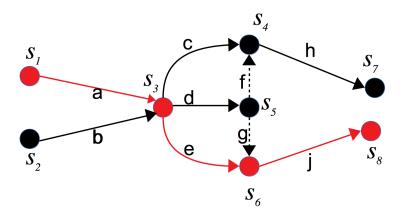

| 1.4  | Signal flow graph model of audio processing system                                 | 25 |

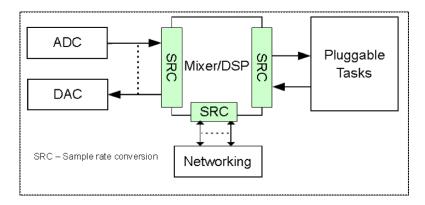

| 2.1  | Digital audio system                                                               | 35 |

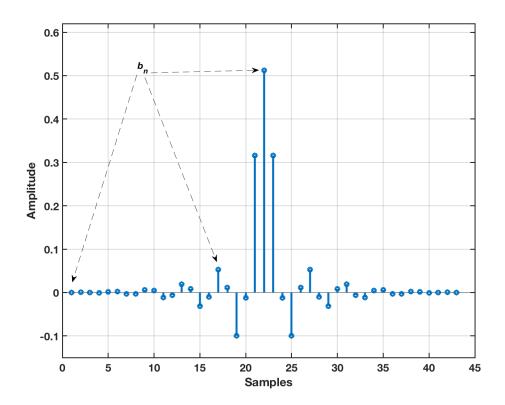

| 2.2  | Typical linear phase FIR coefficients                                              | 46 |

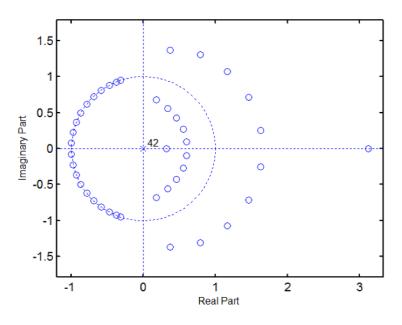

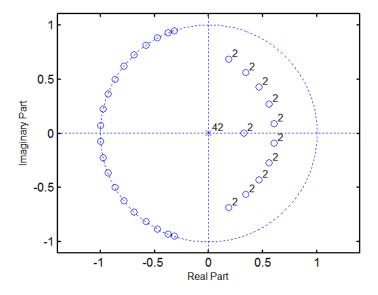

| 2.3  | Roots of H(z) of LP FIR filter                                                     | 47 |

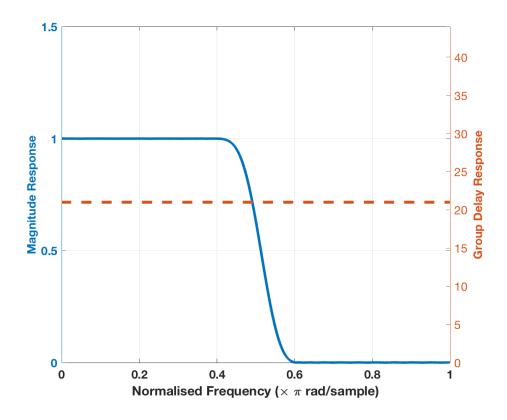

| 2.4  | Magnitude and Group Delay response of a 42 <sup>nd</sup> order Linear Phase Filter | 48 |

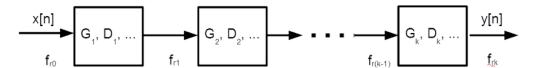

| 2.5  | Multistage filter structure                                                        | 51 |

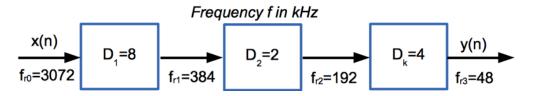

| 2.6  | Example of 64x multistage decimation filter                                        | 52 |

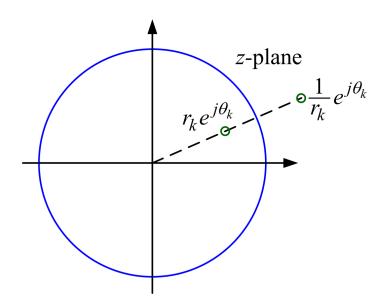

| 2.7  | Zero and reciprocal zero                                                           | 56 |

| 2.8  | MP Filter designed by reflecting zeroes outside unit circle                        | 57 |

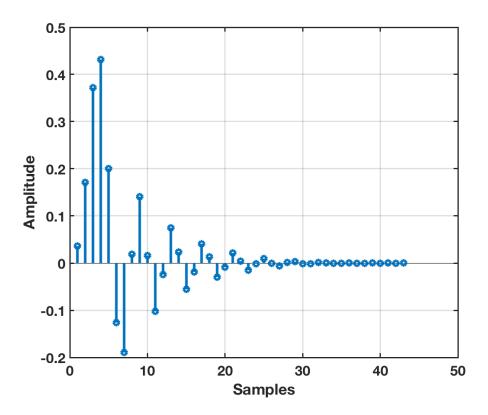

| 2.9  | Transformed Minimum Phase FIR coefficients                                         | 58 |

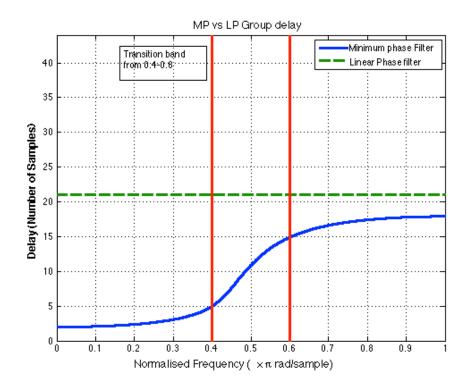

| 2.10 | Group delay of LP and MP filters                                                   | 59 |

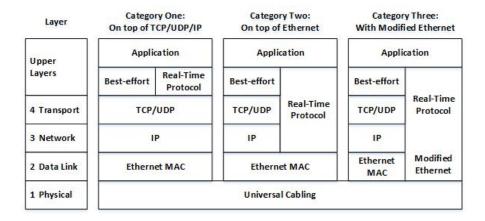

| 2.11 | Different approaches of real-time network protocols                                | 69 |

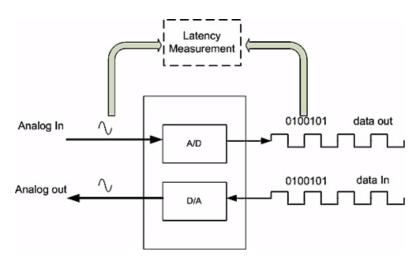

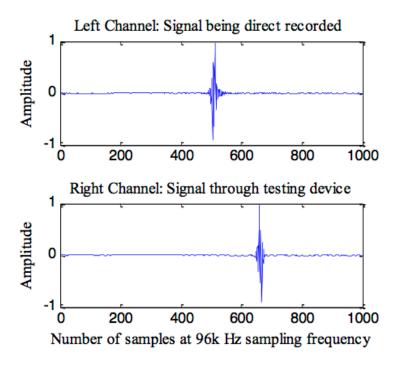

| 3.1  | Codec latency measurement method                                                   | 78 |

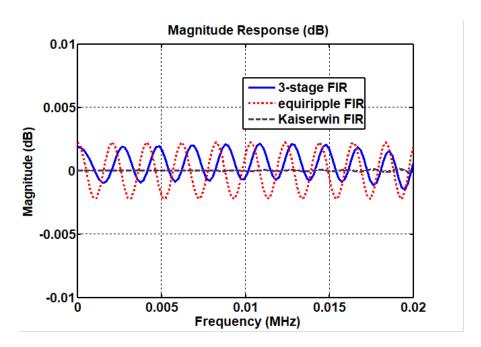

| 3.2  | Magnitude passband of 3-stage FIR, equiripple FIR and Kaiserwin FIR                |    |

|      | filters                                                                            | 93 |

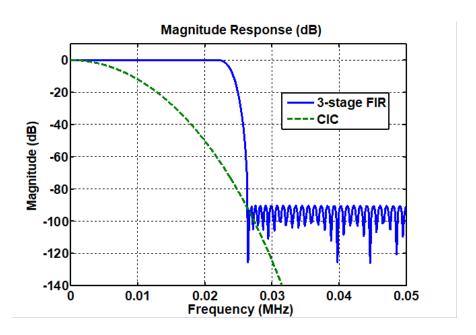

| 3.3  | CIC without compensator in comparison with reference filter                        | 94 |

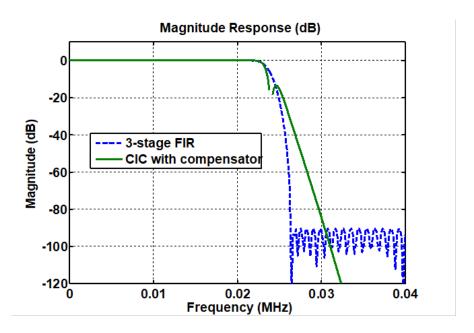

| 3.4  | CIC Filter with compensator in comparison with reference design                    | 94 |

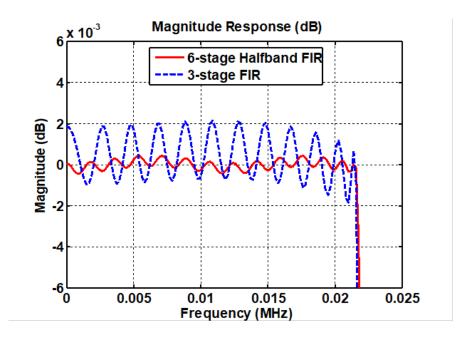

| 3.5  | Passband performance of 6 stage halfband FIR filter in comparison with             |    |

|      | reference design                                                                   | 96 |

| 3.6  | Passband performance of 6-stage elliptic IIR and 6-stage quasi-linear              |    |

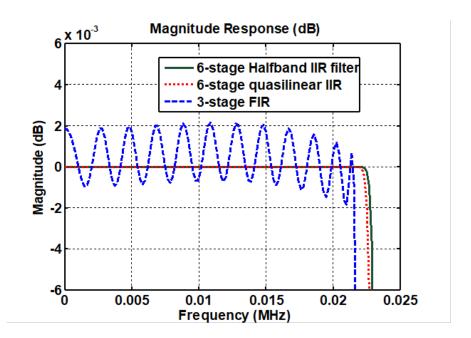

|      | IIR decimator in comparison with reference design                                  | 97 |

| 3.7  | Group delay of 6 stage quasilinear IIR and 6 stage elliptic IIR in com-     |     |

|------|-----------------------------------------------------------------------------|-----|

|      | parison with reference design                                               | 98  |

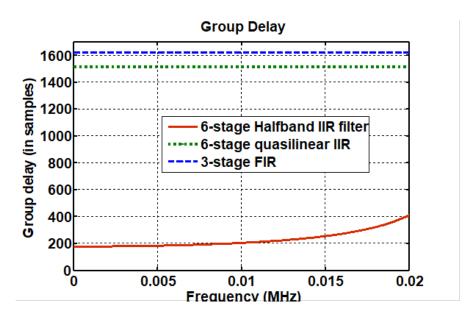

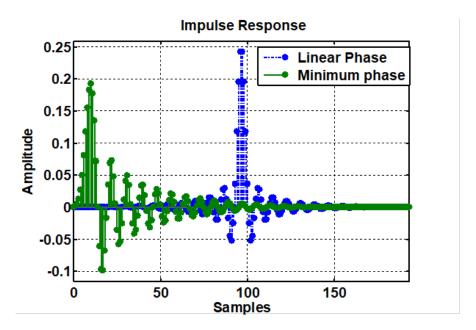

| 3.8  | Impulse responses of minimum phase FIR and linear phase FIR filters .       | 99  |

| 3.9  | Group delay of 6 stage halfband FIR with minimum phase and 3 stage          |     |

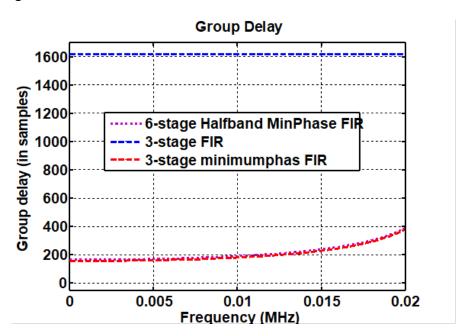

|      | minimum phase FIR                                                           | 100 |

| 3.10 | Group delay of 6-stage halfband FIR, 3 stage minimum phase FIR, and         |     |

|      | 6 stage halfband IIR filters                                                | 102 |

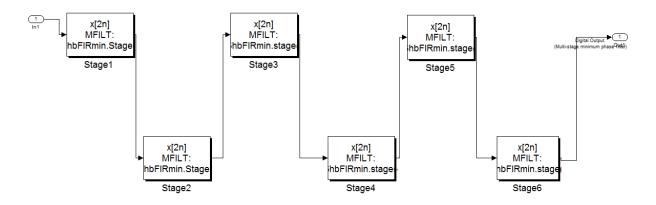

| 3.11 | Simulink model for a subsystem of cascaded 6 stage halfband minimum         |     |

|      | phase filters                                                               | 103 |

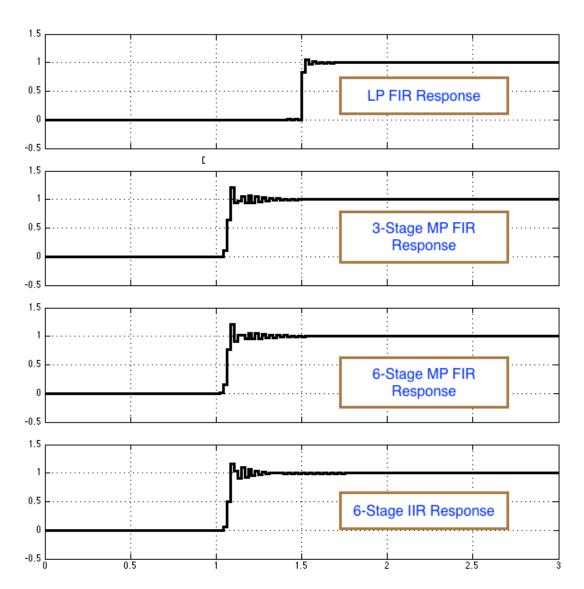

| 3.12 | Simulated step responses of Linear phase FIR, 3-stage minimum phase,        |     |

|      | 6-stage halfband FIR, and 6-stage halfband IIR filters                      | 104 |

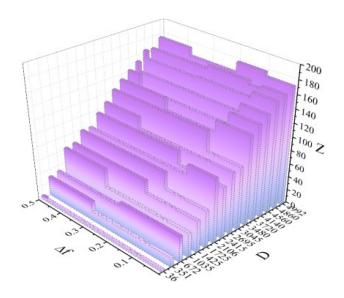

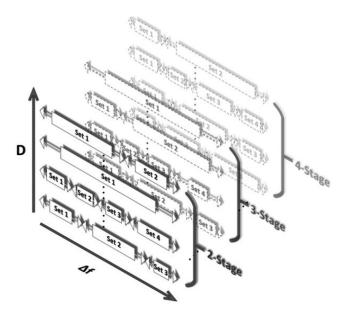

| 3.13 | Real-valued solution sets distribution                                      | 109 |

| 3.14 | Integer solution sets distribution for $D = 2^n \dots \dots$                | 110 |

| 3.15 | Changing of optimal value against $\Delta f$ for some highly composite num- |     |

|      | ber $D$                                                                     | 113 |

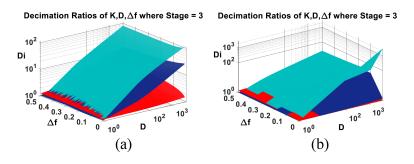

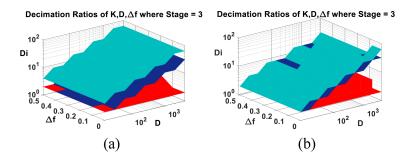

| 3.16 | Depiction of optimal solution sets lookup tables of computational cost      |     |

|      | or memory storage cost                                                      | 113 |

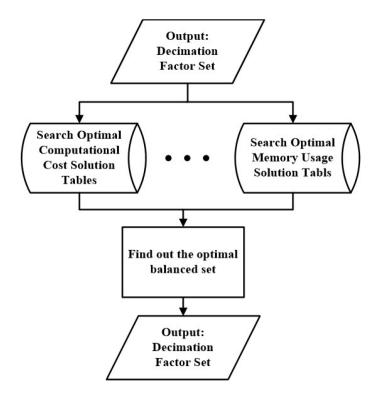

| 3.17 | Flow chart of overall database query algorithm                              | 115 |

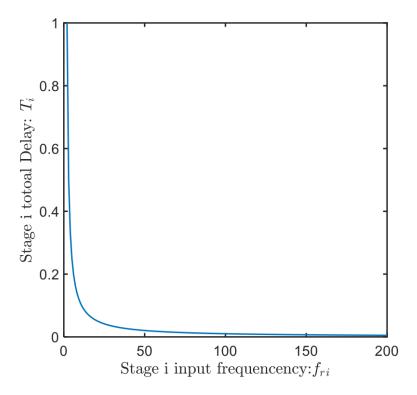

| 3.18 | Delay vs Input Frequency                                                    | 119 |

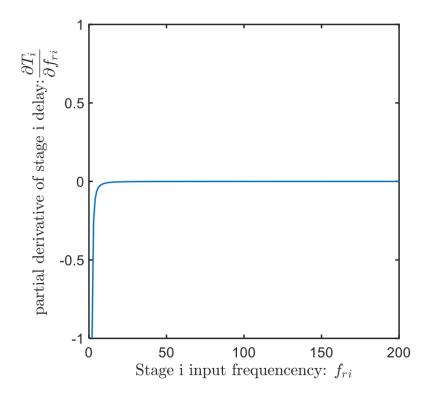

| 3.19 | Partial derivative of single stage delay vs. input frequency                | 120 |

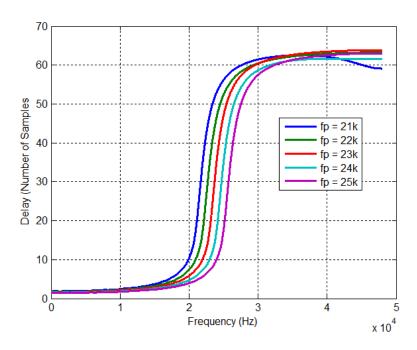

| 3.20 | Different passband corner frequencies with same transition bandwidth .      | 129 |

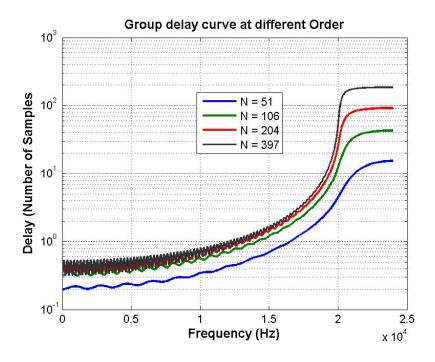

| 3.21 | Group delay of MP filter at different Order                                 | 131 |

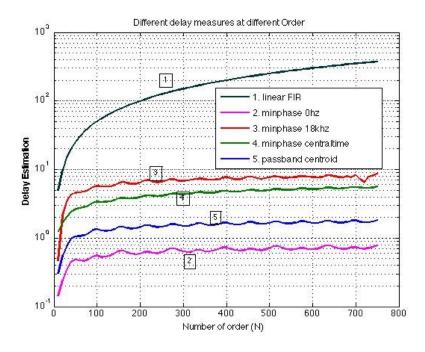

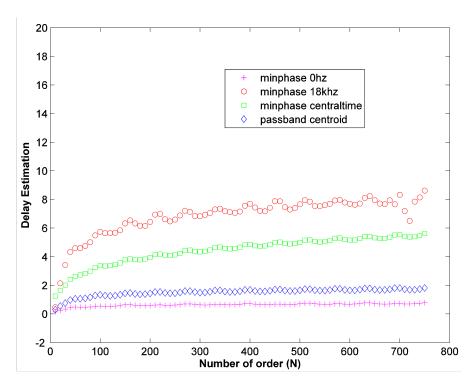

| 3.22 | Different Delay measurements methods vs filter order N $\dots \dots$        | 132 |

| 3.23 | MP filter delay estimation                                                  | 133 |

| 4.1  | Latency measurement from recorded signals                                   | 140 |

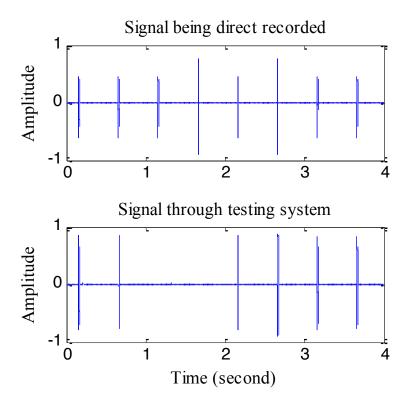

| 4.2  | Loss of pulses in audio processing path at low latency setting              | 149 |

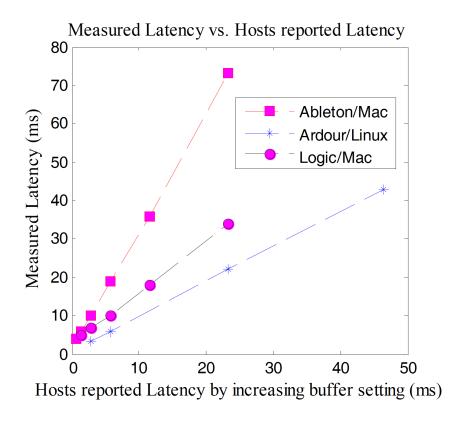

| 4.3  | Measured Latency vs. Hosts reported Latency in millisecond with dif-        |     |

|      | ferent buffer setting                                                       | 153 |

| 4.4  | Periodic Tasks Mapping                                                      | 163 |

| 4.5  | Simulation Results for Set 1                                                |     |

| 4.6  | Simulation Results Set 2                                                    | 166 |

| 4.7  | Simulation Results Set 3                                                    |     |

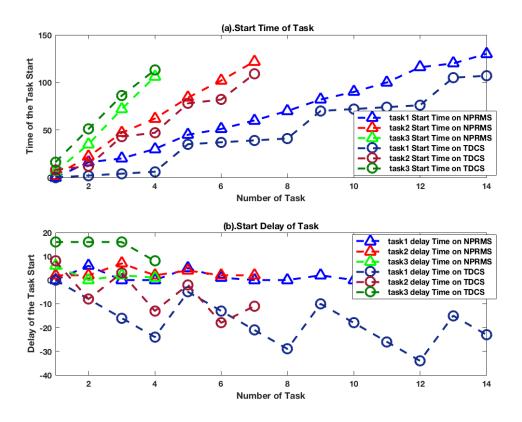

| 4.8  | Task delay and starting time TDCS vs NP-RMS | 168 |

|------|---------------------------------------------|-----|

| 4.9  | Task delay and starting time TDCS vs RMS    | 169 |

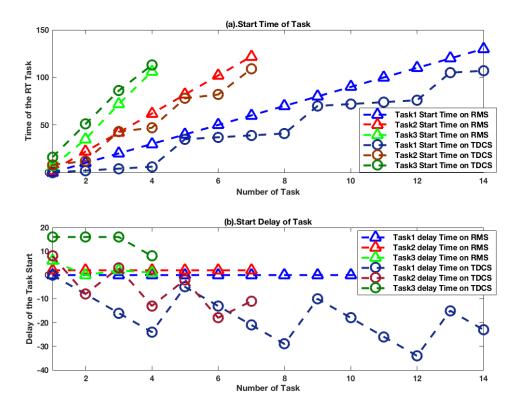

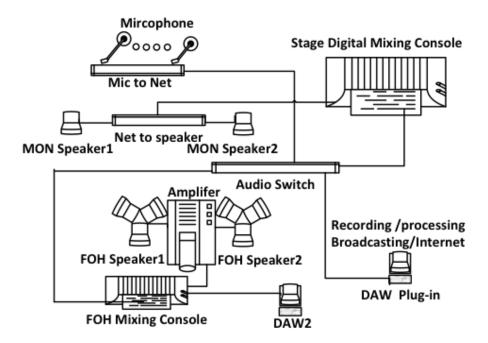

| 4.10 | Task throughput vs CPU utilisation          | 170 |

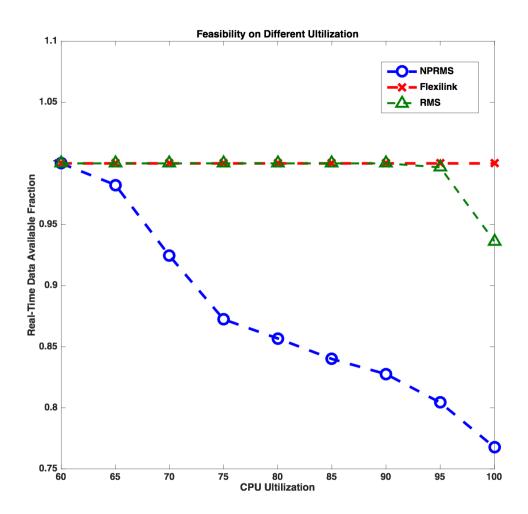

| 5.1  | Audio Processing System                     | 176 |

| 5.2  | Ideal Link for the Traffic                  | 178 |

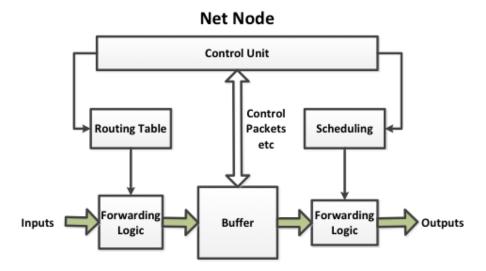

| 5.3  | Architecture of Network Node                | 180 |

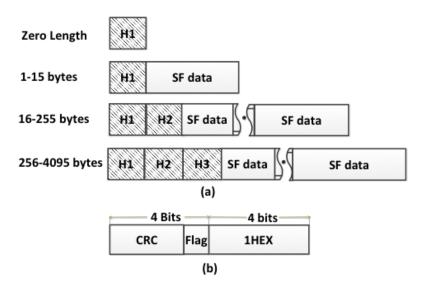

| 5.4  | Header of SF packet                         | 181 |

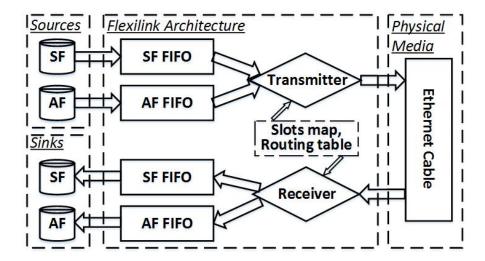

| 5.5  | The MAC layer design of Flexilink           | 182 |

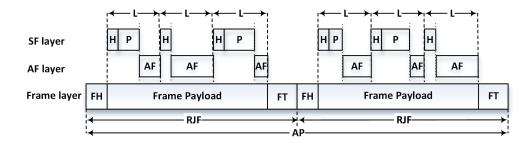

| 5.6  | The layered structure of Flexilink          | 182 |

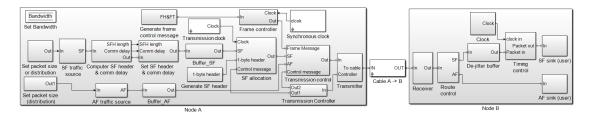

| 5.7  | The Flexilink architecture simulation model | 188 |

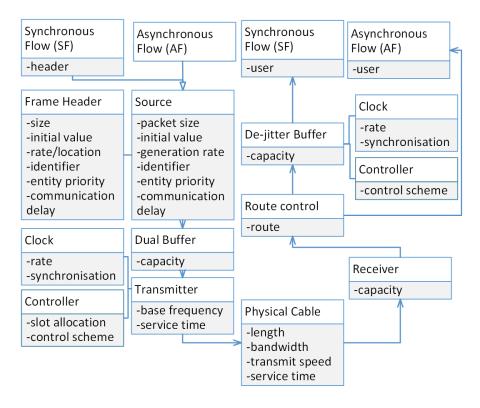

| 5.8  | The parameter list diagram                  | 189 |

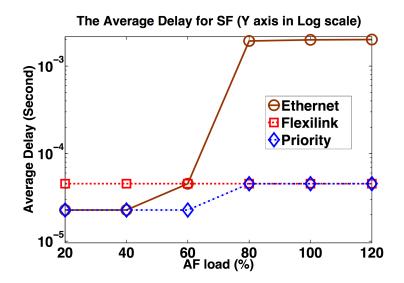

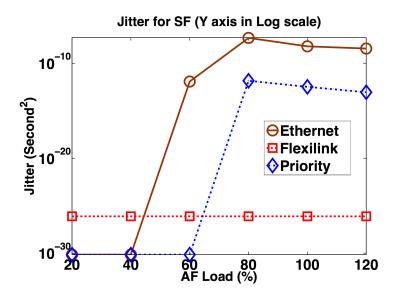

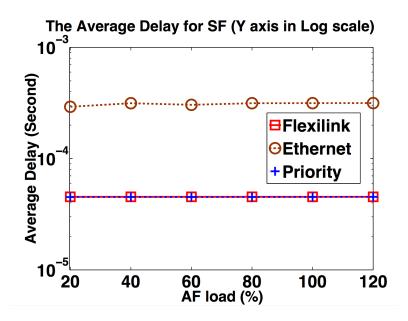

| 5.9  | Average Delay in Case One                   | 193 |

| 5.10 | Jitter in Case One                          | 193 |

| 5.11 | Average Delay for Case Two                  | 195 |

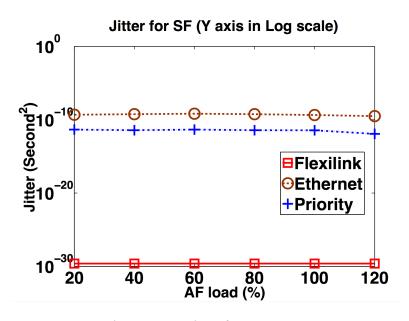

| 5.12 | Jitter for Case Two                         | 195 |

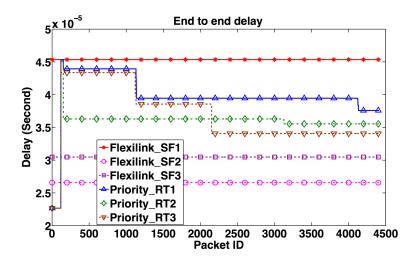

| 5.13 | The E2E delay for each packet for Case Two  | 196 |

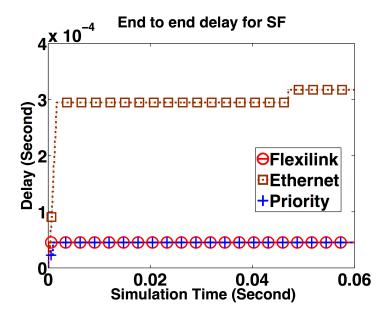

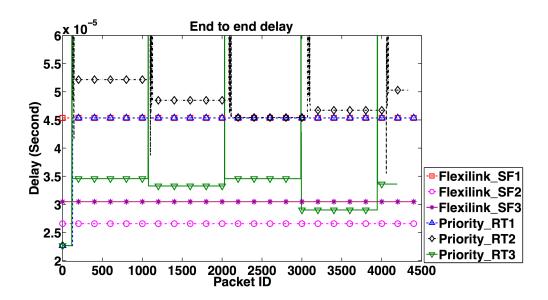

| 5.14 | Detailed E2E delay for SF in Case Three     | 197 |

| 5.15 | Detailed E2E delay for SF in Case Three     | 197 |

| 5.16 | Case Four settings description              | 198 |

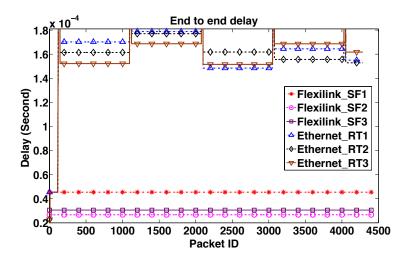

| 5.17 | Detailed E2E delay for SF in Case Four      | 199 |

| 5.18 | Picture of Flexilink switches               | 202 |

| 5.19 | Test Case 1 Proof of Concept Test           | 202 |

| 5.20 | Test Case 2 Stress Test                     | 203 |

| 5.21 | Test Case 1 Flexilink over Gigabit Ethernet | 204 |

| 5.22 | Test Case 2 Stress Test with comparison     | 205 |

## **List of Tables**

| Perceptual Latency Thresholds                                          | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Components latency in digital audio processing chain                   | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Group Delay Audibility Thresholds                                      | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Case 1 vanilla 2.4.17 kernel                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Case 3 low-latency 2.4.17 kernel                                       | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Case 2 preempt 2.4.17 kernel                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| List of Testing Systems                                                | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Group delay of codec obtained from datasheet                           | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Manufacture group delay data and equivalent latency at 48k Hz sampling |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| frequency                                                              | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Measured latency in microseconds at 48k Hz                             | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Latency in microseconds at different sampling                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| frequency and equivalent samples for HD Audio Codec                    | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Filter Design Specifications                                           | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| List of evaluated filters                                              | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Compare single stage FIR filters with multi stage FIR filters          | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Group delay of different evaluated filters                             | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Implementation cost of different filters                               | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Simulated SNR values                                                   | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pseudocode of optimal integer valued solution search algorithm         | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Summary of values of common oversampling-based audio ADC/DAC           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| design specifications                                                  | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Cost balance search algorithm                                          | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Delay effects of number of stage - linear phase                        | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Delay effects of number of stage - minimum-phase                       | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                        | Components latency in digital audio processing chain Group Delay Audibility Thresholds Case 1 vanilla 2.4.17 kernel Case 3 low-latency 2.4.17 kernel Case 2 preempt 2.4.17 kernel List of Testing Systems Group delay of codec obtained from datasheet Manufacture group delay data and equivalent latency at 48k Hz sampling frequency Measured latency in microseconds at 48k Hz Latency in microseconds at different sampling frequency and equivalent samples for HD Audio Codec Filter Design Specifications List of evaluated filters Compare single stage FIR filters with multi stage FIR filters Group delay of different evaluated filters Implementation cost of different filters Simulated SNR values Pseudocode of optimal integer valued solution search algorithm Summary of values of common oversampling-based audio ADC/DAC |

| 3.17 | Simulation result D=32, $k = 1$ and $k = 2$                        |

|------|--------------------------------------------------------------------|

| 3.18 | Simulation result K= 3, D=32                                       |

| 3.19 | Simulation result D=64 K=2                                         |

| 3.20 | Simulation result D=64 K=3                                         |

| 3.21 | Global balanced solution set search algorithm                      |

| 3.22 | Global balanced results                                            |

| 3.23 | Group delay at Same order with different cutoff                    |

| 4.1  | Hardware platform of the test systems                              |

| 4.2  | Cross-reference testing devices                                    |

| 4.3  | List of test operating systems                                     |

| 4.4  | List of audio APIs                                                 |

| 4.5  | List of test Audio Hosts                                           |

| 4.6  | Matrix of Hosts and Operating systems                              |

| 4.7  | Latency of Audacity host with sampling frequency 44100 Hz 146      |

| 4.8  | Low latency hosts with sampling frequency 44100 Hz                 |

| 4.9  | Lowest latencies from the Villain test                             |

| 4.10 | Audio latency with different CPU loads                             |

| 4.11 | Multichannel latency effects                                       |

| 4.12 | Latency measurement of "Max for Live"                              |

| 4.13 | Latency of dedicated digital audio hardware                        |

| 4.14 | Latency measurement of external soundcard M-box 2 mini             |

| 4.15 | Simulation Tasks Sets and CPU utilisation                          |

| 5.1  | The length of a SF packet's header                                 |

| 5.2  | The global parameters                                              |

| 5.3  | Cases introduction                                                 |

| 5.4  | Factors that cause delay                                           |

| 5.5  | Average E2E delay and jitter improvement for Flexilink compared to |

|      | Priority based Ethernet                                            |

| 5.6  | Compare different networking infrastructure designs for audio 207  |

## Acronyms

ADC Analogue to Digital Conversion.

ADAFX Adaptive Digital Audio Effects.

AF Asynchronous Flow.

AVB Audio Video Bridging.

CM Control Message.

**CPS** Cyber-physical system.

**DAC** Digital to Analogue Conversion.

**DAW** Digital Audio Workstation.

**DSP** Digital Signal Processing.

E2E end-to-end.

**EDF** Earliest Deadline First.

FFT Fast Fourier Transform.

FIR Finite Impulse Response.

**GPOS** General Purpose Operating System.

**HAAF** High-resolution Anti-aliasing Anti-image Filter.

**IIR** Infinite Impulse Response.

**LCM** Least Common Multiple.

LP Linear Phase.

MC Mixed-Criticality.

**MP** Minimum Phase.

NP-RMS Non-Preemptive Rate-Monotonic Scheduling.

**OS** Operating System.

**OSI** Open System Interconnection.

PTP Precision Time Protocol.

**RJF** Reduced Jumbo Frame.

**RMS** Rate-Monotonic Scheduling.

**RTP** Real-time Transport Protocol.

RTCP Real-Time Control Protocol.

SF Synchronous Flow.

**SNR** Signal to Noise Ratio.

**STFT** Short-Time Fourier transform.

**SRC** Sample-rate conversion.

TDCS Time Deterministic Cyclic Scheduling.

**TDM** Time Division Multiplexing.

**TSN** Time-Sensitive Networking.

WCET Worst-Case Execution Time.

## Chapter 1

## Introduction

#### 1.1 Motivation

On January 25, 1915, to celebrate AT&T's first transcontinental telephone service, Alexander Graham Bell made a phone call to his former assistant Dr Watson in San Francisco from New York, repeating his famous statement: "Mr Watson, come here. I want you," Dr Watson replied, "It will take me five days to get there now!" [1, 2]. This is because this telephone call was made from about 4134km away.

When the room temperature is at 20°C, the sound speed<sup>1</sup> is around 343.3 m/s [3], and the delay from a sound source to a listener is about 2.91 milliseconds(ms) per meter.

Sound transducers, which convert audio signals into electric waves, drastically increase the speed of dissemination of the signal to near the speed of light. The propagation speed of electromagnetic signals within copper is about 0.66 to 0.88 of the speed of light.

Imagining a sound is loud enough to be heard, it takes approximately 4.5 hours to transmit from San Francisco to New York, whereas with the telephone line, it takes at best 12ms on each way.

The audio and music industry is notoriously conservative when embracing new digital technology that potentially disrupts the 'vintage' of nostalgic analogue sound. Despite

$<sup>^{-1}</sup>C_s = 331.4(1 + 3.66 \times 10^{-3} \times \theta)^{1/2} \approx 331.4 + 0.6 \times \theta \, (m/s)$ , where  $\theta$  is temperature in Celsius.

this, computer music and digital audio effects have become mainstream since Moorer made the prediction in 2000 for future digital audio technology [4], as well as the audio industry has shifted from the mainframe to do-it-yourself (DIY) culture with miniaturised and democratised live applications [5].

Due to the rapid development of computer science and the Moore's law in the semiconductor industry, using a commodity computer with a Digital Audio Workstation (DAW) has become common practice. High-Resolution, low power audio ADC/DAC devices have become a necessity. Also, audio transmission is moving towards converged data communication networks along with other types of traffic. These advancements and conveniences sometimes bring more and unpredictable delay. The latency problem has often been discussed in various audio/music communities, second only to the complaint of 'cold' digital sound.

Human ears are sensitive to delays in many situations. For example, a standard telecommunication delay must be less than 250ms both ways to avoid deteriorating the conversation significantly [6], whereas high-quality music ensemble over network shall have end-to-end delay less than 25ms [7]. The human auditory system is also incredibly adaptive to the environment. Perhaps it is the unpredictable delay that makes people most uncomfortable with. In music ensembles, excessive delay between two audio sources makes musicians feel uneasy and hard to synchronise, and variations of delay makes bands difficult to coordinate.

From the system engineering point of view, the typical audio processing chain includes capturing, processing, transmission, routing and playback. The digital advancement enhances all parts of audio processing chain in aspects of conversion quality, processing capability, and cost-effectiveness of hardware and software. Meanwhile, the system latency seems not to be improved at a similar pace. On the contrary, lots of 'guesswork' and 'rule of thumb' of delay estimations are used in a system design.

### 1.2 Aim and Objectives

It is important to have accurate time delay parameters within a system design formula that help to predict the known delay effects to the users and audiences. In this research, we aim to answer the following research questions:

- 1. What are the sources of delay in the digital audio processing chain?

- 2. Can we accurately estimate the delay when designing a digital audio system?

- 3. Can we adopt deterministic approach in the system design to minimise the delay in the digital audio system?

The challenge of this research is to establish the deterministic and quantitative framework for evaluating the delay as a time parameter in system design from the bottom up. Related research in this field is often statistical and empirical, treating time delay as an uncontrollable parameters [8, 9, 10]. However, we aim to understand the root of this problem and propose reasonable solutions by fulfilling the following objectives:

- Investigate and identify the sources of latency in the digital audio system chain.

- Investigate and test the delay of high-resolution ADC/DAC for audio conversion.

- Test the delay of audio processing in Digital Audio Workstation (DAW) and operating systems.

- Investigate the latency issues of audio networking.

- Develop accurate delay estimation methods for digital filters in ADC/DAC.

- Form a reduced group delay High-resolution Anti-aliasing Anti-image Filter (HAAF) design.

- Propose a new OS scheduling framework that is capable of doing low latency processing.

- Develop a deterministic audio networking architecture with supporting of convergence.

Evaluate the performance of proposed methods and frameworks by using simulation and experimental tests.

#### 1.3 The Method of Research

#### 1.3.1 The Systems Engineering Point of View

In the digital age, there is an increasing human expectation of the 'smooth' and 'quick' response from digital systems, especially when dealing with interactive audio and video applications. In other words, being 'real-time' is not good enough. Users require a satisfactory responsiveness of the system - a predictable low latency.

In engineering science, latency is a measure of time delay experienced in a system and can be defined as the time delay between the input and output signals of a real-time signal processing system. Different applications have different latency requirements for real-time signal processing. Live audio processing can be considered as real-time audio processing with latency constraints. In a timing-driven system design and validation methodology for multi-input and multi-output scenario [11], the quantifiable constraints can be

- 1. On the same input to or output from a task: *a rate constraint*.

- 2. Between two different inputs or outputs: *an input correlation constraint* and *an output correlation constraint*.

- 3. From an input of a task to its output: *a latency constraint* or *an arbitrary separation constraint*, which is useful to define *response time constraints*.

The latency requirement in live audio processing is equivalent to the "response time constraint" from the system design point of view.

#### 1.3.2 The Causes of Latency and Latency Taxonomy

The overall latency is caused by different components in the digital audio processing chain, and there are different classifications of the causes of latency in literatures range from 2002 to 2016 [12, 13, 14, 15, 16, 17, 18, 19]. However, in principle, they can be categorised into the following three factors:

- (a) Physical propagation latency (speed of sound and speed of light):  $G_p$ .

- (b) Buffering digital samples caused latency:  $G_b$ .

- (c) The phase delay of digital filters (group delay):  $G_d$ .

The delay components described in the literature in relation to these three factors can be depicted in the following Figure 1.1.

Figure 1.1: Different descriptions of the causes of latency in audio systems

Among these three factors, often (b) 'buffering' is the means to mitigate the problem of non-deterministic characteristics of some parts of the system. For example, buffering is used in computer sound subsystem as **digital buffering audio input/output hardware**, in the network interface to carry out **packetisation**, **serialisation**, **de-jitter**, and **queuing tasks**, in the bus system, and for the operating system scheduling algorithms. In other cases, buffering is used to accumulate a block of samples for further operation

such as frequency based processing (Latency of the application in out of frequency domain). The delay of a digital filter (c) can be observed from  $\Delta\Sigma$  ADC/DAC devices because of their internal decimator and interpolator filters. Many DSP algorithms and SRC processes use these types of digital filters.

Some latency components are the combination of these three factors, for example, DSP algorithms that involve block based processing (b) and digital filters (c). Asynchronous SRC (ASRC) uses FIFO (b) and multiple FIR filters (c). Network delay also includes (a).

#### 1.3.3 Reduce the Latency and Design Trade-Off

The overall latency can be reduced by minimising the latency of each component in the audio processing chain. However, in practice, there is often considerations and trading-off of design requirements over the whole system. For example, one can use ADC/DAC architectures other than  $\Delta\Sigma$  based. However, the high resolution cannot be achieved in a cost effective way, and the analogue circuit and hardware cost can be very expensive in doing so. Therefore the effort can be made to use reduced group delay decimation and interpolation filter design for  $\Delta\Sigma$  based ADC/DAC.

To reduce the buffer size, the system can be carefully designed to ensure that the real-time audio processing path is dealt with a time-deterministic manner. That requires not only fast enough computation, but also meeting the specific time deadline. This implies avoiding the use of non-real-time operating systems in the time critical path.

In addition, the DSP algorithms need to be designed in mind with minimum buffer requirements such as:

- 1. Use time domain sample based process, such as filter banks, rather than the frame based approach, such as FFT based processes [20, 21, 22].

- 2. Use reduced filter delay design such as minimum phase design, or linear phase filter that is optimised towards group delay.

In the large scale audio venue employing multiple audio channels, audio networking is a essential component. Current audio network technologies, such as AES50, and Ethersound, can achieve very low latency using time division multiplexing (TDM) methods, but these solutions require the sample rate of multiple channels to be rectified into the one sampling frequency or integer multiplication of that sampling frequency. Thus the SRCs are needed, which introduces additional latency that may be larger than the network latency itself.

#### 1.3.4 Report Accurate Latency

There are misconceptions about zero delay design in the audio system. Bufferless processing often is regarded as 'zero delay' without considering the group delay caused by phase response. The delay of audio plugins and various DSP algorithms is either only reported incorrectly (using only buffer delay) or regarded as 'inherent delay' that is not accurately estimated.

The modern audio system is becoming complex with a large number of components and the accumulated delay can be significant. 'Live' audio systems that require processing audio input and output within certain time constraints because of human perception and interaction, are indeed examples of a Cyber-Physical Systems (CPS). Here, the current latency problem of the digital audio system is similar to that which exists in CPS, which is lack of timing accuracy reporting from different levels of abstract layers [23]. For example, the system can be described as a layered structure as in Figure 1.2.

Figure 1.2: Different layers of delay in digital audio system

Often the lower layers of the system such as network delay and operating system delay

cannot be deterministic. They are often statistically measured as QoS values, examples like "98% tasks can be scheduled within  $200\mu s$ " or "20ms when the network is not congested". These ambiguities affect the upper layer system design in terms of timing accuracy. The example of the latency of web audio is hard to manage due to it builds on top of various intermediate software layers [24].

#### 1.3.5 Group Delay and Buffering Delay

Group delay and buffering are two distinguishable delay factors. Group delay is significant if it is caused by high order digital filtering. It is intrinsic to digital filters' time domain performance. Buffering is used for many different reasons. However, it is fundamentally to mitigate the non-deterministic time events. It is often set up for the worst case scenario. With propagation delay, they all contribute to the overall system latency.

To the best knowledge of the author, audio latency has not been clearly defined and evaluated at the system components level, and there is lack of low level design methods to optimise the system latency with consideration of various trade-offs of design options for the systems. This research investigates these areas using the methodology described in the following section.

### 1.3.6 Digital Audio System Signal Flow

We can model a typical digital audio system using the block diagram as in Figure 1.3. Figure 1.3 describes the general case of a digital audio system that can support live audio processing.

Figure 1.3 shows the typical components in a digital audio system with their logic and physical connections. The multichannel audio sources can be recorded in live and input from the block 'P1' or the off-line sound files in block 'P2'. The 'Routing Matrix' acts as the audio bus to route audio channels according to the user configurations. Some of the audio sources are routed to the feature extraction and control block 'B3'. The output audio signals are transmitted to the different destinations.

Figure 1.3: Digital audio system

For analysing latency along, the block diagram can be further refined using the signal flow graph that has been developed by Mason in 1956 [25]. This can be modelled as a 'signal flow graph' shown in Figure 1.4. The solid lines represent the audio signal flows and the dashed lines represent the control message flows. To use the system for low latency processing, a sub-route can be identified as the time critical path.

Figure 1.4: Signal flow graph model of audio processing system

The system can be represented as a graph  $G_{sys} = (V, E)$ , V are vertices, and E are edges. In this example, we have  $V = \{S_1, S_2, S_3, ... S_8\}$ ,  $E = \{a, b, c, ... j\}$ . The time of system input and output that the user is interested in can be regarded as the critical path of the system as  $C_{sys} \subseteq G_{sys} = (V_c, E_c)$ . where  $V_c$  and  $E_c$  represent the vertices and edges of critical path subset. In this example  $V_c = \{S_1, S_3, S_6, S_8\}$ ,  $E = \{a, e, j\}$

Let  $G_{bi}$ ,  $G_{di}$  be the buffering and the group delay of node  $S_i$ .  $G_{pi}$  is the propagation delay between two connected points  $S_i$ . We can define the interested delay of the digital audio system as Equation (1.1):

$$D_{sys} = \sum_{i \in V_c} (G_{bi} + G_{di}) + \sum_{i \in E_c} G_{pi}$$

(1.1)

For audio signal transmitting within a limited geographic area such as within computers and peripherals, the  $G_p$  is in the range of picoseconds that can be ignored.

#### 1.3.7 System Engineering Approach

The model in Figure 1.4 and Eq. (1.1) shows the system level latency and how it is composited. In this work, we investigate three main subsystems in the digital audio processing chain including ADC/DAC, operating system and audio networking. Both white box and black box approaches are used to carry out the detailed tests of some components latencies for part of the system with the properly designed methodologies. The results and findings then lead to the analytical approaches to the sources of the problem. Using the white box approach, we analyse and propose new mathematical models, optimisation methods, and a new system architecture, that overcome the problem of ambiguous reports of system latency values between system layers and provide a deterministic time domain performance.

Therefore, in this research we investigate the roots of audio processing latency using a bottom-up and deterministic approach, to identify and simplify the common factors that affect the overall latency, and to evaluate and estimate the latency quantitatively. In short, the method of the research is to make Eq. (1.1) determinable and try to minimise each term of it.

### 1.4 The Scope of the Research

The methods adopted in this research do not try to address the system design question, which is how to produce bespoke digital systems that satisfy the latency requirements. However, this research investigates the latency problems in three of the most significant parts of digital audio processing chain:

- 1. Latency caused by the  $\Delta\Sigma$  based audio ADC DAC.

- 2. Latency caused by the General Purpose Operating System (GPOS) based audio processing platform.

- 3. Latency in the converged network infrastructure for the professional audio transmission.

Capturing (ADC) and playing back audio (DAC) are two most front-end interfaces between the analogue world and the digital world. We shall ask these questions: Is there any delay when we capture and playback the audio signal in the high-resolution digital era? What causes the delay? Can it be reduced?

The advantage of GPOS based system is to processing digital audio with tremendous flexibility and convenience. There are versatile DSP algorithms and almost infinite combinations of them to process audio. We focus on the fundamental questions that cause the processing delay in GPOS. Why do we need to wait for a number of audio samples to be accumulated (buffered) before processing them? Does processing algorithms cause the delay? Can all complexing processing tasks be scheduled properly so that the outcome delays are predictable?

In the audio networking area, is it the right direction to use a common networking infrastructure to transmit audio? What are the problems with it? How can we improve it so that the delay of audio transmission can be predictable and minimised? Can audio transmission co-exist with other types of traffic? How to transmit the multichannel audio streams each with different bandwidths and sampling rates?

These questions are reviewed and researched with consideration of human perception of delay and interactions, which give us the guidance of the magnitude of each problem

and the time constraints that we can work on. The outcomes of research are not limited to these three aspects. They address the more fundamental causes of latency, and the concepts and theory can be applied in broader perspectives of the signal processing chain.

### 1.5 The Organisation of the Thesis

Chapter 2 reviews the state of the art of current research concerning system latency in audio processing including the perception of latency and the tolerable latency of human interaction; the typical latency values in the digital audio processing chain; OS processing delay; the group delay of high order filters; and networking delay. Other relevant delay components such as the algorithm delay, the architecture delay are also discussed.

Chapter 3 presents the test of  $\Delta\Sigma$  ADC/DAC delay and an evaluation of time domain properties of different multistage multirate filters that cause the delay in  $\Delta\Sigma$  ADC/DAC. A theory of accurate prediction of delay and formalised delay as an objective function of multistage design parameters. A simplified method to find the overall balanced design that takes delay into account. An objective measurement of delay in minimum phase system is also presented with a quantitative analysis.

**Chapter 4** presents the updated latency measurements of the desktop OSes with DAWs. Particularly, the latency issues under heavy CPU load caused by audio processing are discussed when using commodity General Purpose Operating System (GPOS). A new time deterministic OS scheduling framework specifically designed for low latency audio processing is proposed. The simulation results in comparison with classic rate monotonic scheduling are presented and discussed.

**Chapter 5** proposed a new low latency audio network architecture and protocols that can support different audio sampling rates in conjunction with other non-real-time data. The proposed architecture provides the deterministic audio data delivery that can achieve the stability that below audible jitter. The software simulation and hardware prototype testing of it are also presented.

#### 1.6 Contributions

- Chapter 1: A new latency taxonomy based on meta research and system analysis.

- Chapter 3: A latency measurement of modern audio  $\Delta\Sigma$  ADC/DAC and a comprehensive evaluation of time domain performance of different types of multistage and multirate filters for  $\Delta\Sigma$  ADC/DAC.

- Chapter 3: A simplified optimal design sets search method for multistage and multirate filter design for  $\Delta\Sigma$  ADC/DAC.

- Chapter 3: Formalisation of group delay as an objective function of multistage filter design parameters and proposed a new multi-objective optimisation method to design filters for  $\Delta\Sigma$  ADC/DAC including overall delay.

- Chapter 3: A set of new objective measurements formulas for Minimum Phase (MP) filters and the evaluation over High-resolution Anti-aliasing Anti-image Filter (HAAF).

- Chapter 4: A comprehensive latency test using modern DAWs and OSes with consideration of internal audio load and cross-adaptive effects.

- Chapter 4: Time Deterministic Cyclic Scheduling (TDCS) a new scheduling framework for low latency audio processing with simulation results.

- Chapter 5: Design new low latency deterministic network protocol Flexilink.

- Chapter 5: A comprehensive performance evaluation of Flexilink against other priority-based network architectures with simulation and hardware test.

#### 1.7 Associated Publications

Chapter 3, Section 3.1 was published as

Y. Wang, "Latency Measurements of Audio Sigma Delta Analogue to Digital and Digital to Analogue Converts," in 131st AES Convention, New York, NY, USA, 2011. [26]. The author of the thesis wrote and did the main research.

Chapter 3, Section 3.2 was published as

Y. Wang and J. Reiss, "Time Domain Performance of Decimation Filter Architectures for High Resolution Sigma Delta Analogue to Digital Conversion," in Audio Engineering Society Convention 132, 2012. [27].

The author of the thesis wrote and did the main research. The other author had an editing and supervising role.

First part of Chapter 3, Section 3.3 was published as

• X. Zhu, Y. Wang, W. Hu, and J. D. Reiss, "Practical considerations on optimising multistage decimation and interpolation processes," in Digital Signal Processing (DSP), 2016 IEEE International Conference on, 2016, pp. 370–374. [28].

The author of the thesis wrote the main paper, discovered the regularity of optimal solution sets, and proposed the simplified search and balanced design algorithm. Xiangyu Zhu implemented factorisation algorithm as the core part of the simplified search method, as well as other implementations and obtaining the testing results. Other authors had an editing and supervising role.

Chapter 4, Section 4.1 was published as

• Y. Wang, R. Stables, and J. Reiss, "Audio Latency Measurement for Desktop Operating Systems with Onboard Soundcards," in Audio Engineering Society Convention 128, 2010. [12].

The author of the thesis wrote and did the main research. Other authors had an editing and supervising role.

Chapter 5, Section 5.1 was published as

• Y. Wang, J. Grant, and J. Foss, "Flexilink: A unified low latency network architecture for multichannel live audio," in 133th Audio Engineering Society Convention, 2012. [29].

The author of the thesis wrote the main paper. The design of new network protocol and architecture were the results of the discussion with John Grant, who shared the experi-

ences and ideas from his audio over ATM work and audio networking standardisation work. Other authors had an editing and supervising role.

Chapter 5, Section 5.2 was published as

• Y. Song, Y. Wang, P. Bull, and J. D. Reiss, "Performance Evaluation of a New Flexible Time Division Multiplexing Protocol on Mixed Traffic Types," in Advanced Information Networking and Applications (AINA), 2017 IEEE 31st International Conference on, 2017, pp. 23–30. [30].

The author of this thesis contributes the main idea of simulation, the design of simulation model, and the main testing strategy. Yangyang Song did the implementation and the test. Yangyang Song also written the first draft with author's help in structure and final modification. Other authors had an editing and supervising role.

### 1.8 Unpublished Results

Second part of Chapter 3, Section 3.3.

• The quantitative analysis of delay of high-resolution anti-aliasing and anti-image filter.

Chapter 4, Section 4.2.

• Time Deterministic Cyclic Scheduling (TDCS) - A new scheduling framework for real-time Multimedia OS

Chapter 5, from architecture design to new hardware testing results.

• Towards true convergence, the architecture and performance evaluation of dynamic TDM system: Flexilink.

We aim to publish these results in the near future.

#### 1.9 Other Relevant Publications

There are other research work the author contributed. They helped to reinforce the findings of this research, to understand the general problem in current audio processing software and hardware architecture, and to inspire the proposed solutions:

- Y. Wang, X. Zhu, and Q. Fu, "A Low Latency Multichannel Audio Processing Evaluation Platform," presented at the Audio Engineering Society Convention 132, 2012. [31].

- N. Jillings and Y. Wang, "CUDA Accelerated Audio Digital Signal Processing for Real-Time Algorithms," in Audio Engineering Society Convention 137, 2014. [32].

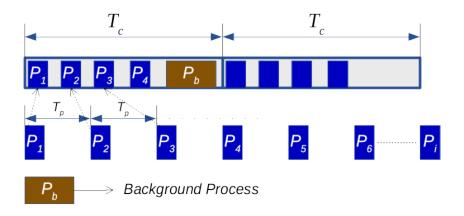

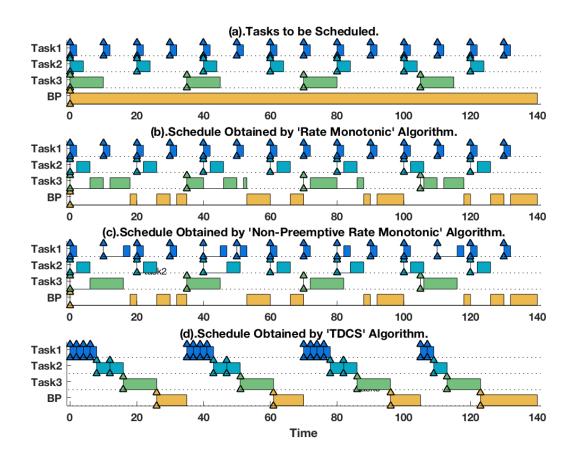

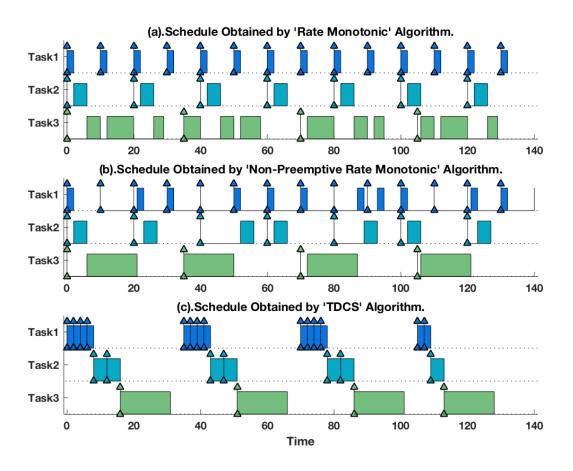

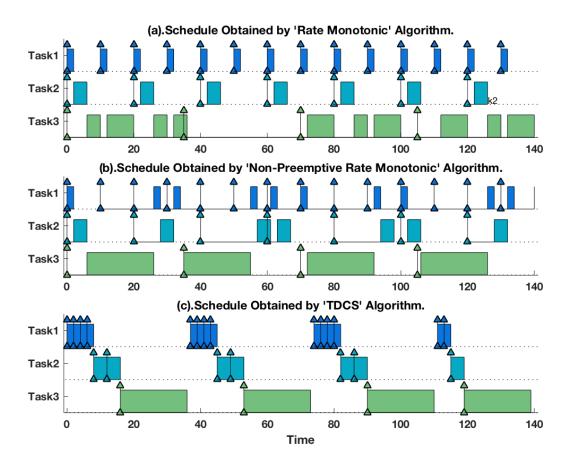

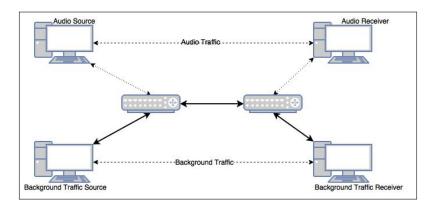

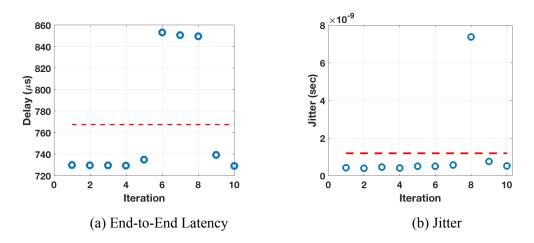

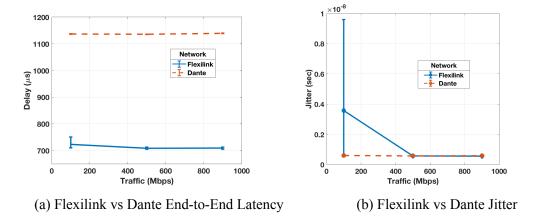

- N. Jillings, Y. Wang, J. D. Reiss, and R. Stables, "JSAP: A Plugin Standard for the Web Audio API with Intelligent Functionality," in Audio Engineering Society Convention 141, 2016. [33].